Vous suivez désormais

Erreur de suivi de l'utilisateur.

Cet utilisateur n'utilise pas les utilisateurs à le suivre.

Vous suivez déjà cet utilisateur.

Votre plan d'adhésion ne permet que 0 suivis. Améliorez ici.

Ne suit désormais plus

Erreur lors de l'arrêt du suivi de l'utilisateur.

Vous avez désormais recommandé

Erreur lors de la recommendation de l'utilisateur.

Une erreur a eu lieu. Veuillez rafraîchir la page et réessayer.

E-mail désormais vérifié.

rawalpindi,

pakistan

Il est actuellement 7:25 PM ici

Rejoint le octobre 15, 2011

0 Recommandations

Elecguru011

@Elecguru011

0,0

0,0

83%

83%

rawalpindi,

pakistan

N/A

Travaux complétés

N/A

Suivant le budget

N/A

Dans les temps

N/A

Taux de réembauche

Embedded Design Enigneer with expertise in FPGA and DSP Systems Engineering

Contactez Elecguru011 concernant votre travail

Connectez-vous pour discuter de tous les détails via la messagerie.

Portfolio

Portfolio

25Hz Transmitter Coil

25Hz Transmitter Coil

25Hz Transmitter Coil

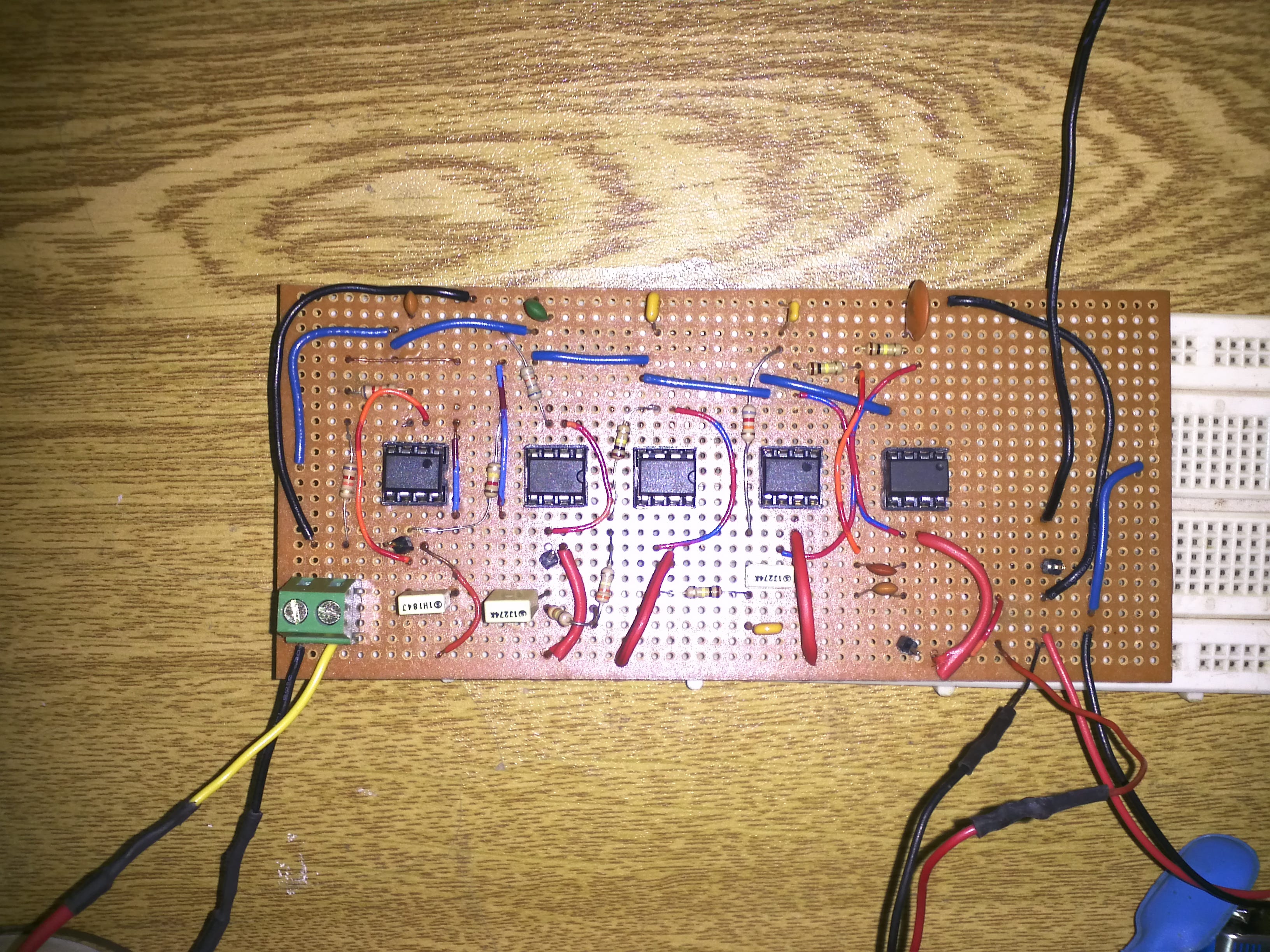

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

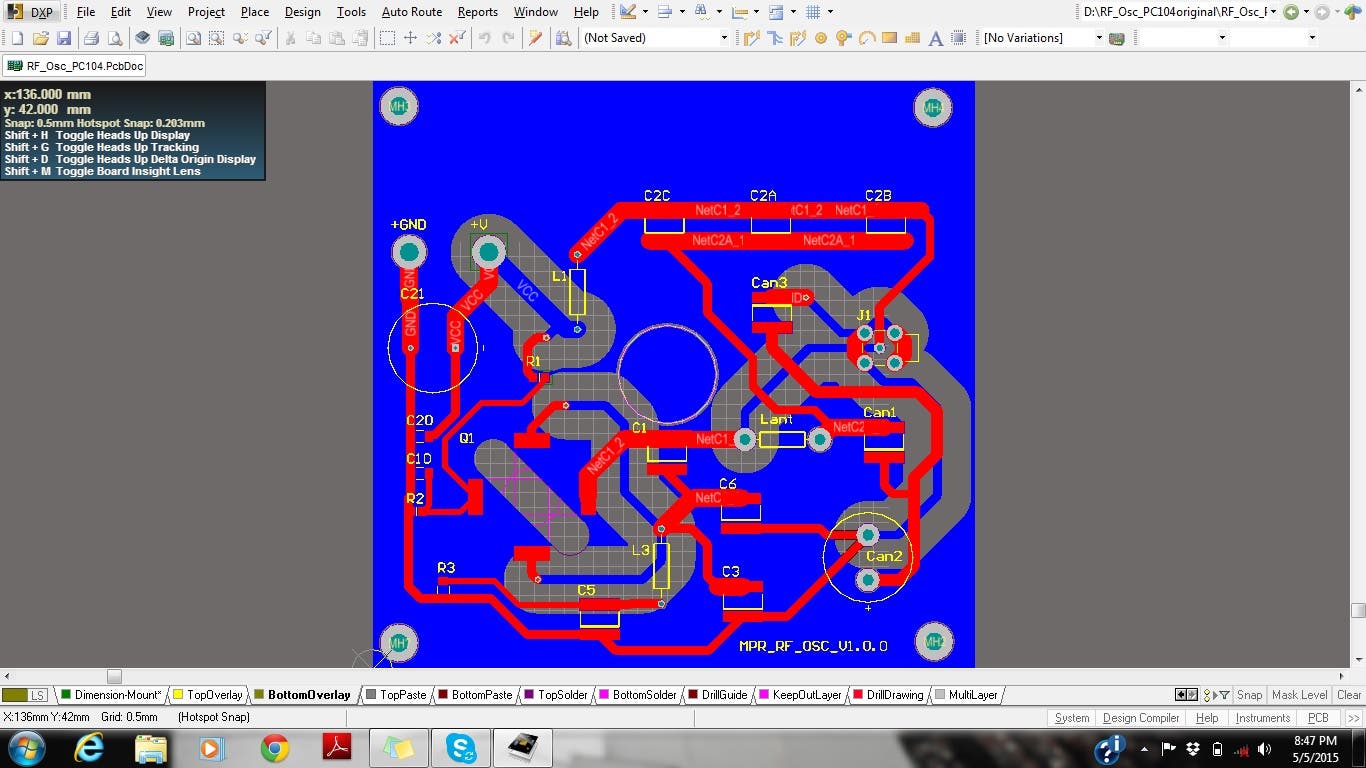

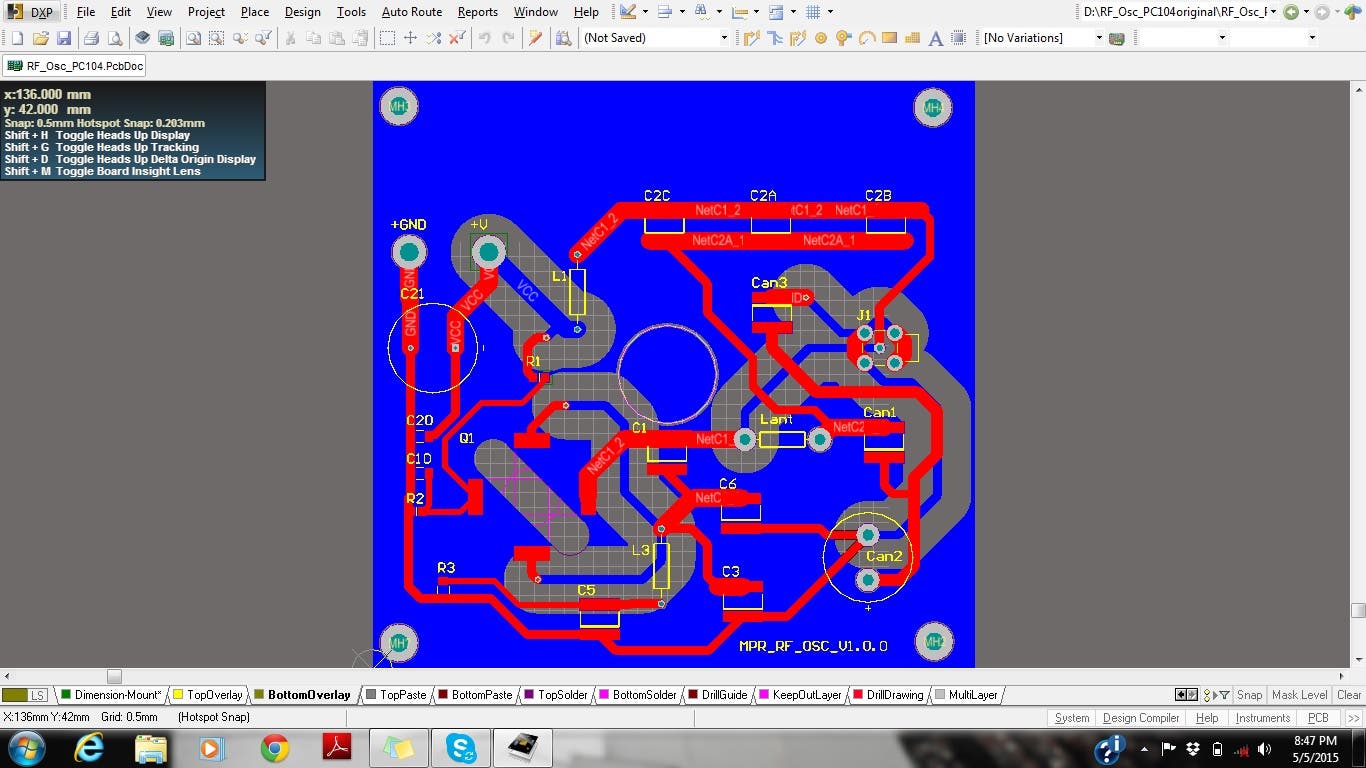

RF Oscillator

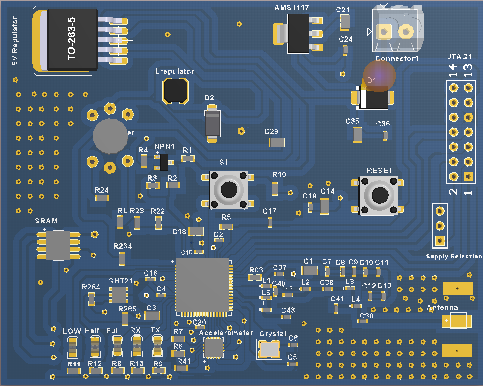

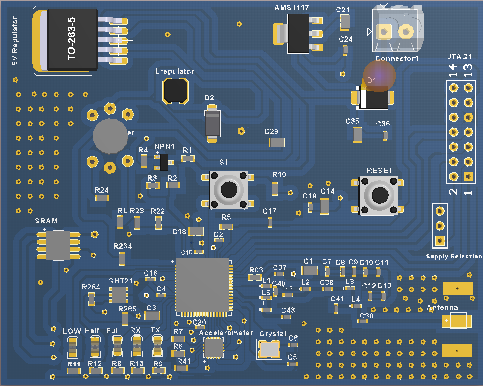

DASH-7 Wireless Board

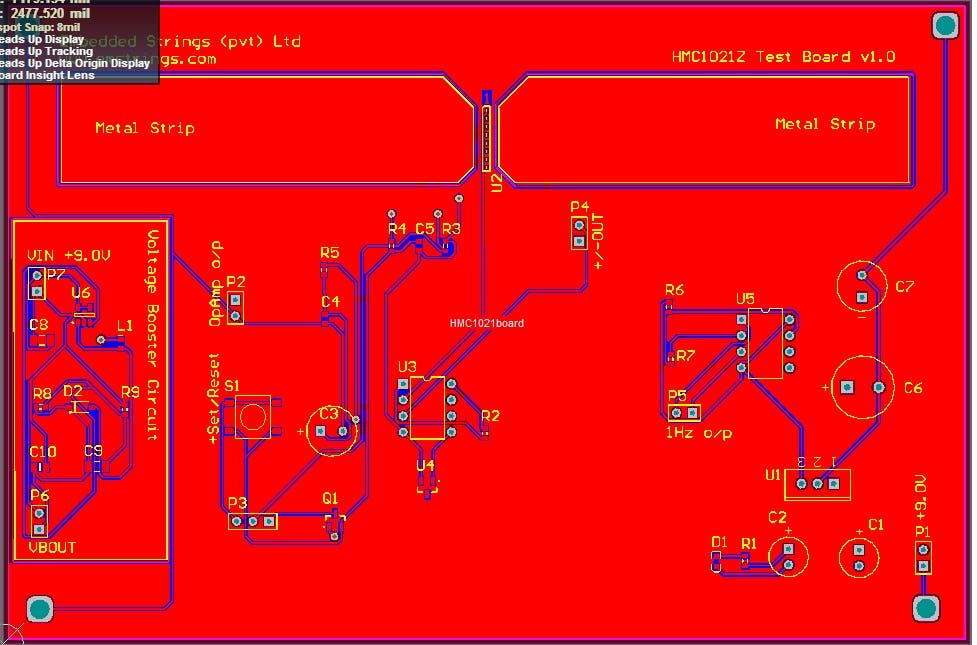

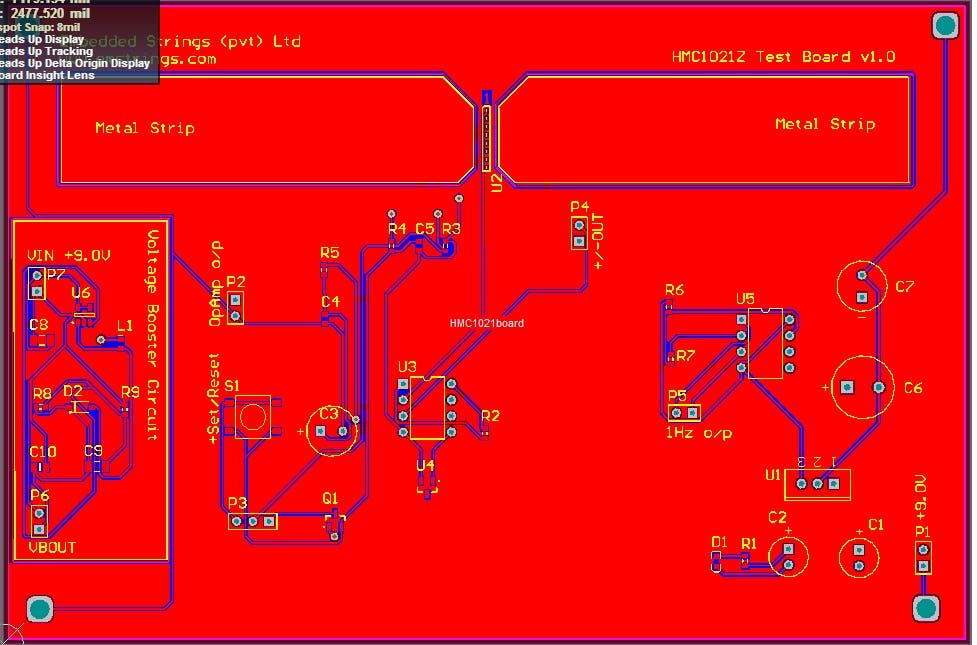

Altium PCB Design

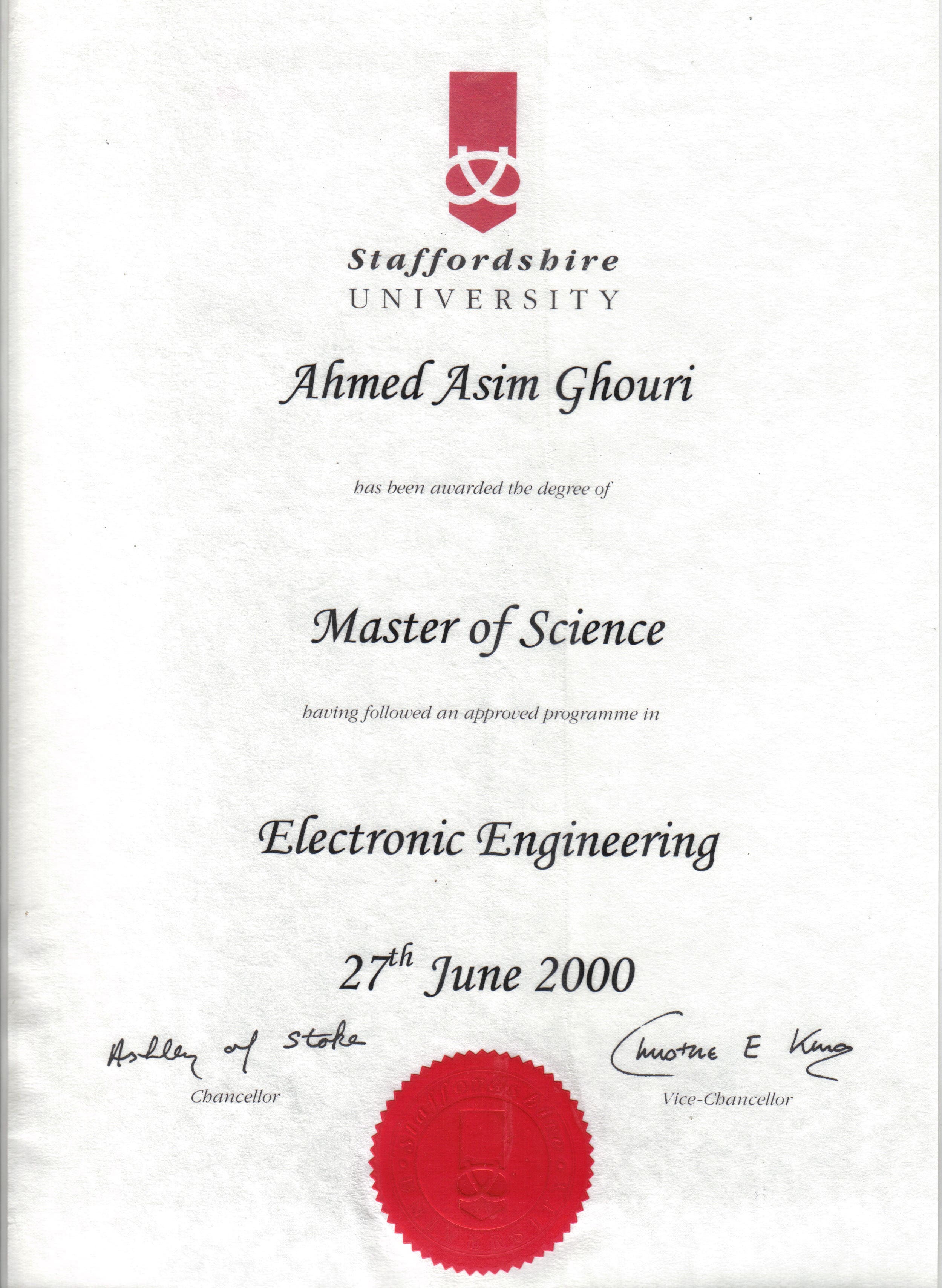

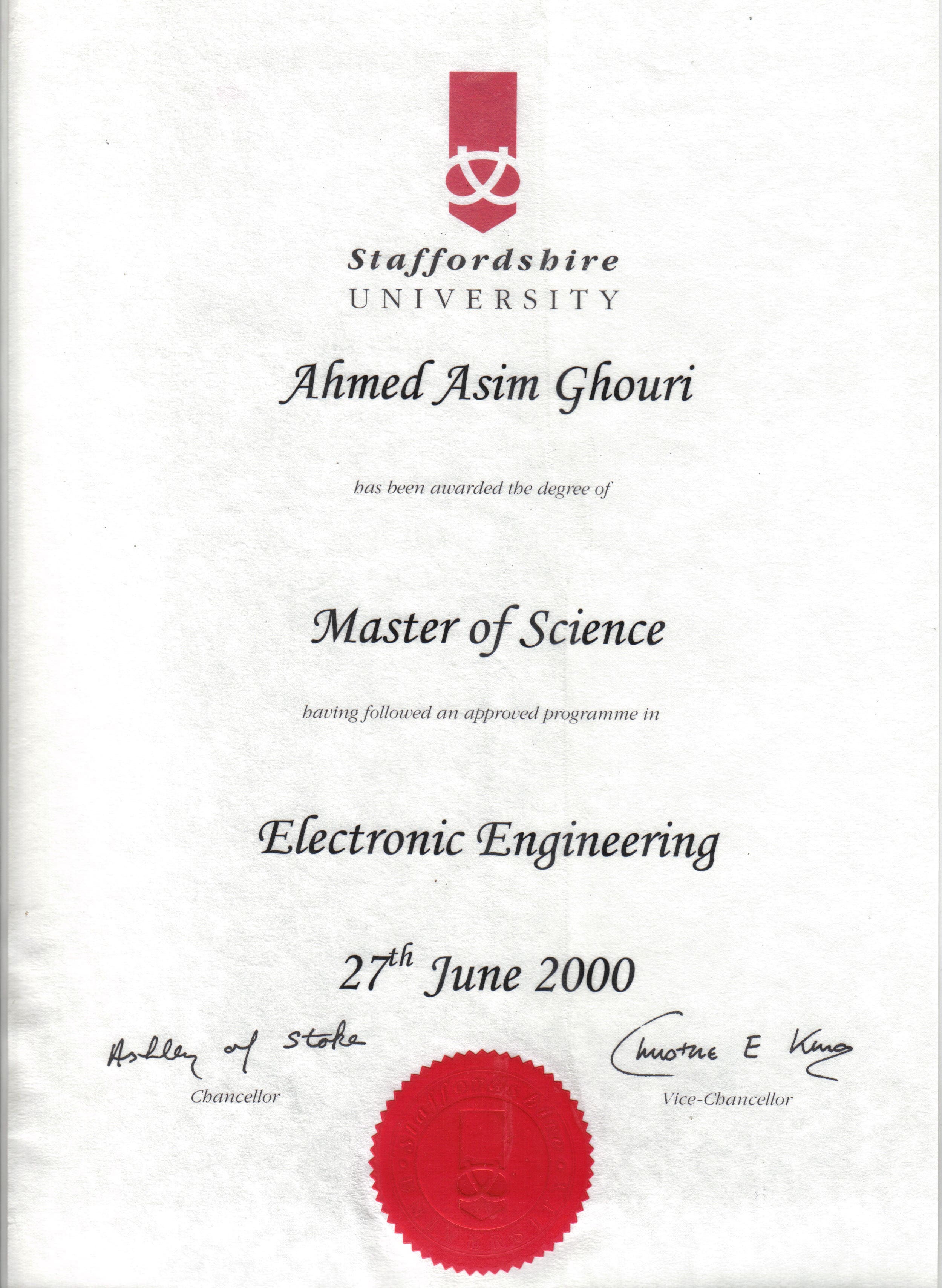

Masters of Electronics Engineering

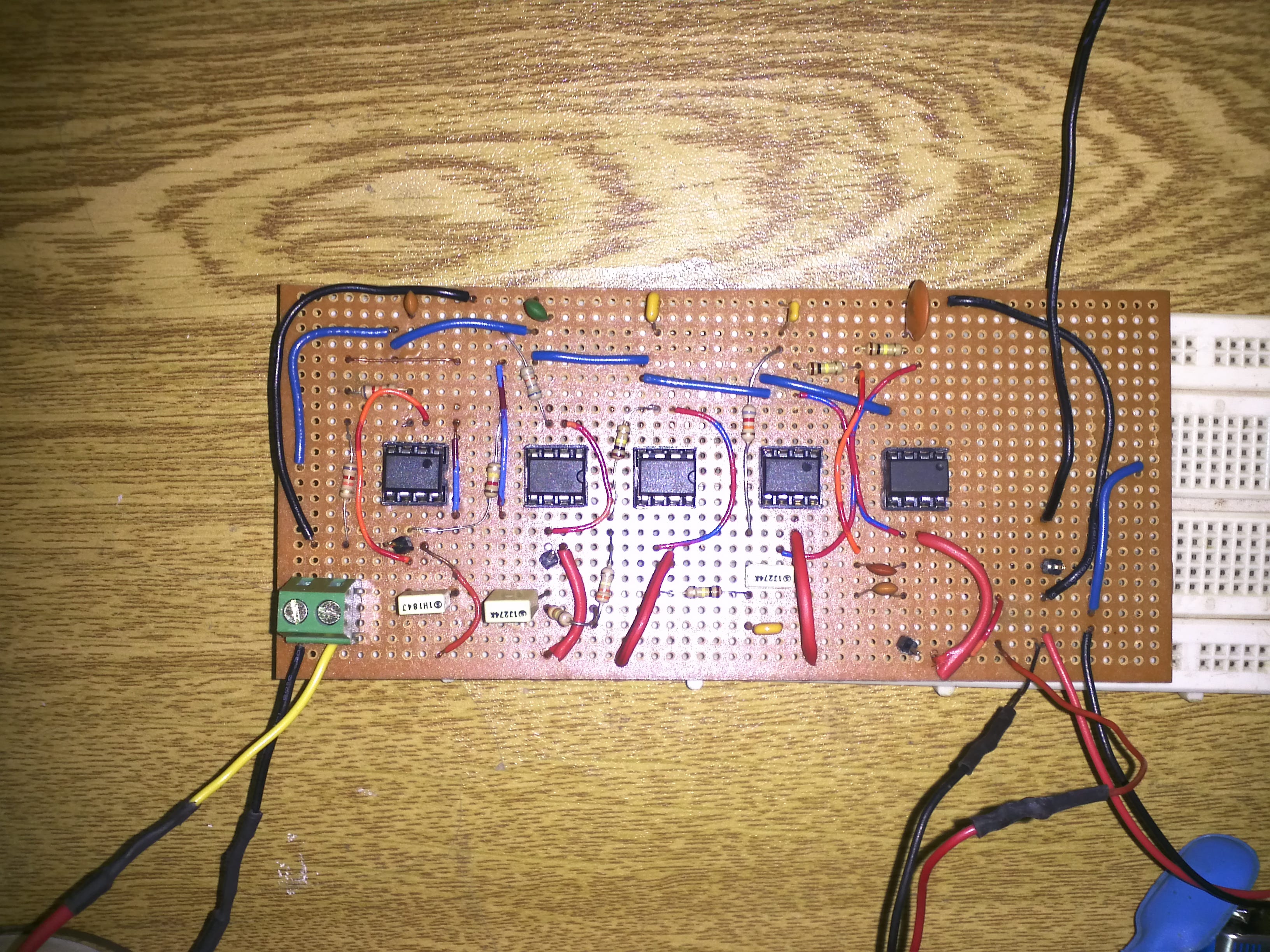

25Hz Transmitter Coil

25Hz Transmitter Coil

25Hz Transmitter Coil

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

RF Oscillator

DASH-7 Wireless Board

Altium PCB Design

Masters of Electronics Engineering

Commentaires

Modifications enregistrées

Montre1 - 1 sur 1 commentaires

$50,00 USD

Verilog / VHDL

FPGA

•

Expérience

Project Engineer

juil. 2015 - Jusqu'à présent

Embedded Systems design , FPGA and PIC Microcontroller based hardware design . Firmware and Software design and Systems analysis using Matlab.

Team Lead

janv. 2012 - déc. 2014 (2 ans, 11 mois)

I worked as Hardware Design group Team Lead , developed modules for wireless sensor network.

Digital and Analogue Design Engineer

mai 2010 - déc. 2011 (1 an, 7 mois)

FPGA Hardware Design of Satellite Communication system.

Éducation

M.Sc Telecommunication Engineering

(2 ans)

MSc Electronics Engineering

(3 ans)

Qualifications

DSP Systems Engineering

University of California , Irvine

2012

Digital Signal Processing fundamentals, DFT,FFT , Digital Filter modelling and simulation using Matlab, FIR and IIR filter implementation on FPGA

Winner Best Design

Cypress Semiconductor

2004

Reconfigurable Logic using PSOC

Publications

OTDR Implementation on FPGA

Embedded Strings (pvt)Ltd

Optical Time Domain Reflectrometery

In optical fiber communication, optical time domain reflectometery (OTDR) is a commonly used technique for characterization and fault location of optical fiber transmission systems. It involves measuring the fraction of a probe pulse that is scattered back (by Rayleigh scattering) from a silica fiber. Because of the very small levels of backscatter in single-mode fiber at long wavelengths, very sensitive optical detection is necessary to achieve adequate range performa

Audio Signal Processing

Ahmed A Ghouri

An audio signal frequency range is from 20Hz to 20Khz. In a music sample 20Khz bandwidth is required to encompass all harmonics. Although natural sounding speech only requires about 3.2Khz . Telecommunication systems typically operate with a sampling rate of about 8 kHz, allowing natural sounding speech, but greatly reduced music quality.

Here we are proposing a FPGA based audio signal filtering system which is reconfigurable and can be used as a Processing Engine to reduce background noise from a musi

Contactez Elecguru011 concernant votre travail

Connectez-vous pour discuter de tous les détails via la messagerie.

Vérifications

Certifications

Meilleures compétences

Parcourir les freelances similaires

Parcourir les présentations similaires

Invitation désormais envoyée !

Merci ! Nous vous avons envoyé un lien par e-mail afin de réclamer votre crédit gratuit.

Une erreur a eu lieu lors de l'envoi de votre e-mail. Veuillez réessayer.

Chargement de l'aperçu

Permission donnée pour la géolocalisation.

Votre session de connexion a expiré et vous avez été déconnecté. Veuillez vous connecter à nouveau.